Hardware Verification Group Home > Research > Methodologies and Frameworks >

Surrogate based Optimization and Verification of AMS Designs

Ibtissem Seghaier, Mohammed Hussein Zaki and

Sofiene Tahar

Contact:

seghaier@encs.concordia.ca

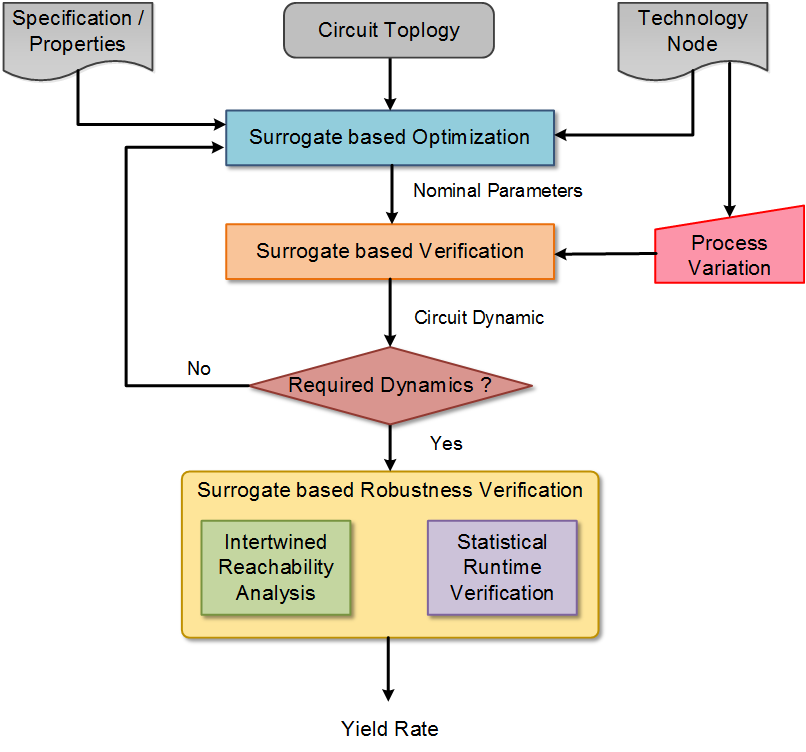

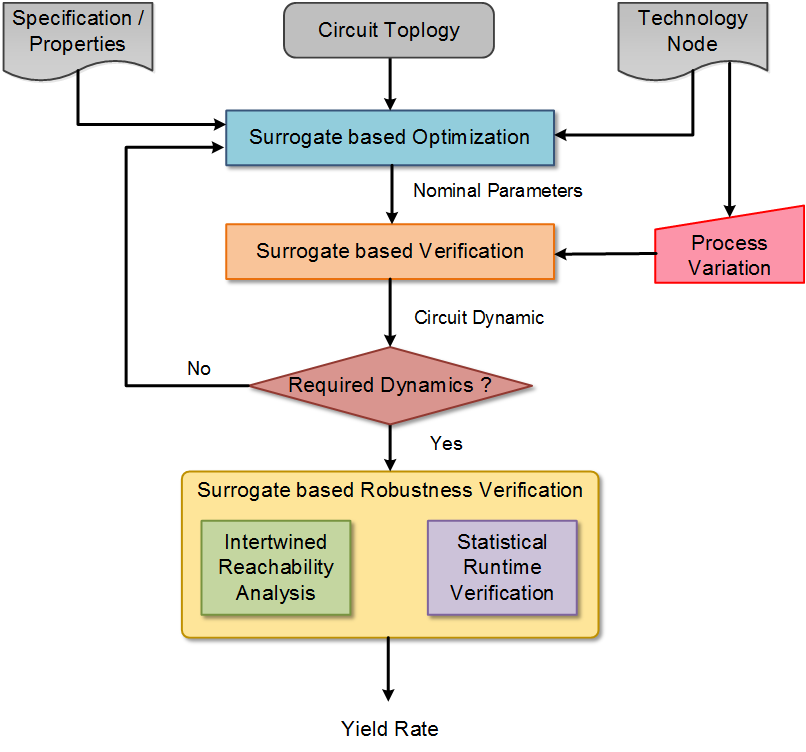

To design circuits, current industrial practices rely heavily on simulation based verification and knowledge based

optimization techniques. However, such techniques lack mathematical rigor which is necessary to catch up with the

growing design complexity besides being computationally intractable. In this research project, we propose a framework to induct the

optimization and verification of Analog and Mixed Signal (AMS) designs as depicted in the figure below. First, we perform a surrogate based optimization method with an interplay between a circuit model and a behavioral model of an AMS design.

Then, a surrogate based qualitative verification is conducted to ensure a non chaotic behavior of the

circuit for the computed nominal parameters. Finally, a surrogate based quantitative verification is developed to prove the circuit robustness to process variation.

To illustrate the usefulness of the proposed framework, we are tackling various applications including oscillators, Analog to Digital Converters (ADC) and Phase Locked Loops (PLL).

Journal Papers

I. Seghaier, M. H. Zaki, and S. Tahar: Mating Sensitivity Analysis and Statistical Verification for Efficient Yield Estimation; IEEE Transactions on CAD of Integrated Circuits and Systems (TCAD), under review, January 2018, pp. 1-14.

Conference Papers

I. Seghaier and S. Tahar: Intertwined Global Optimization based Reachability Analysis, LNCS International Conference on Verification and Evaluation of Computer and Communication Systems (VECoS'17),

Montreal, Quebec, Canada, August 2017, pp. 139-154.

I. Seghaier, M. H. Zaki and S. Tahar: Cross Recurrence Verification Technique for Process Variation-Resilient Analog Circuits,

IEEE International Symposium on Circuits and Systems (ISCAS'16), Montreal, Quebec, Canada, May 2016, pp. 1294-1297.

I. Seghaier, M. H. Zaki and S. Tahar: A Statistical Approach to Probe Chaos from Noise in Analog and Mixed Signal Designs,

IEEE Annual Symposium on VLSI (ISVLSI'15), Montpellier, France, July 2015, pp. 237-242.

I. Seghaier, M. H. Zaki and S. Tahar: Statistically Validating the Impact of Process Variations

on Analog and Mixed Signal Designs, ACM Great Lakes Symposium on VLSI (GLSVLSI'15), Pittsburgh, Pennsylvania, May 2015, pp. 99-102.

Technical Reports

I. Seghaier and S. Tahar: Intertwined Global Optimization based Reachability Analysis of Analog and Mixed Signal Designs,

Technical report, Department of Electrical and Computer Engineering, Concordia University, January 2018. [23 Pages].